## 第2章

デジタル信号処理に不可欠な

乗算器を使いこなす

— HDLによる記述のしかたと FPGA 開発ツールの設定

田中良平

本章では、FPGAにおける乗算器の活用法を解説する。最近のFPGAは、低成本・ファミリでは乗算器を、高性能ファミリでは積和演算機能を持つDSPブロックを搭載している。デジタル信号処理のように、多くの演算を行うアプリケーションの設計では、乗算器を効果的に活用することで、高い性能を実現できるようになる。

(編集部)

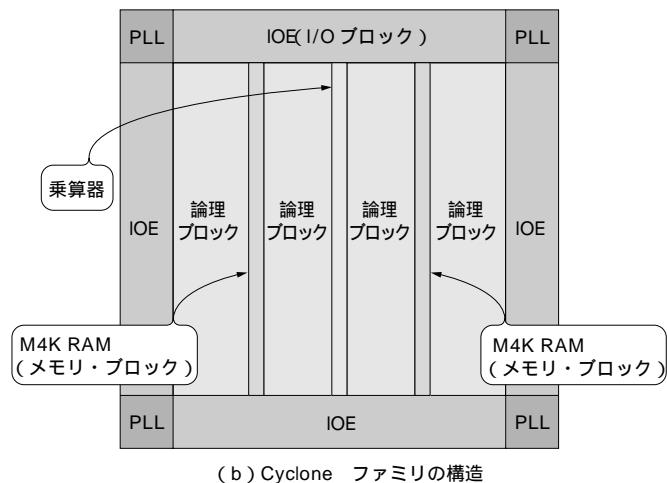

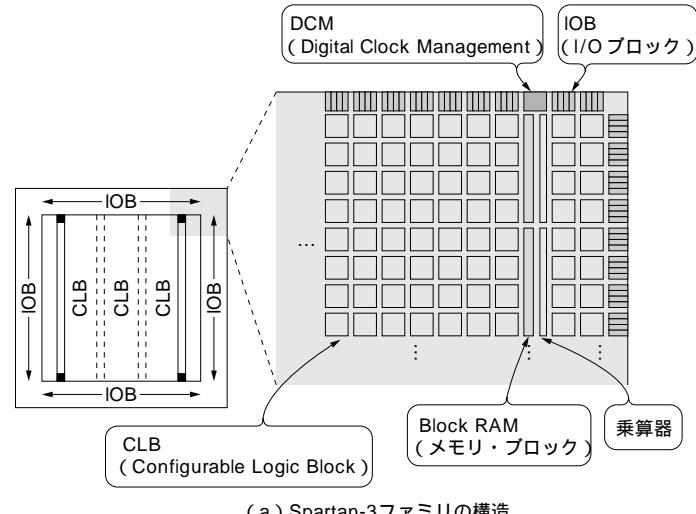

最近のFPGA(field programmable gate array)は、単なるプログラミング可能な論理ブロックのかたまりではなくなります。あらかじめハード・ワイヤード論理で作られた乗算器、クロック管理、メモリなどの機能が組み込まれています(図1)。

乗算器は論理ブロックを使えば実現可能です。しかし、演算精度を上げようとすると多くの論理ブロックを消費し、遅延も大きくなってしまいがちです。これに対して、ハード・ワイヤード論理の乗算器であれば、シリコン上で構成できる最高の性能が保証されることになります。アプリケーション回路の設計において、特定の機能についての回路規模や動作速度への影響を気にする必要がなくなることは、大きなメリットになります。あらかじめ組み込まれた機能を活用することは、これからはとても重要になるでしょう。

主要なFPGAが持つ、これらの非論理機能を表1にまとめます。例えば、米国Xilinx社のFPGA「Spartan-3 ファミリ」には、18ビット×18ビットの演算ができる4～104個の乗算器が搭載されています(表2)。「Virtex-4 ファミリ」ではこのハード・ワイヤード論理の乗算器に加算器とマルチプレクサも加わったDSPブロックに進化しています。

図1

FPGAの構造

(a)は、Xilinx社のSpartan-3 ファミリのうちの XC3S200 から XC3S2000 までの構造を示している。XC3S4000 と XC3S5000 では、左側のチップ全体の図の点線で示した列の部分(中央の CLB の中)もメモリ・ブロック( Block RAM )になる。XC 3S50 では、乗算器や Block RAM は左側の1列だけになる。(b)は Altera社の Cyclone ファミリの EP2C20 の構造を示している。

## 1 乗算器の使いかた

デジタル信号処理( DSP )アプリケーションにおいては、非常に多くの乗算処理が行われます。乗算回路はどうしても回路規模が大きくなりがちです。そこで、あらかじめ FPGA に搭載された乗算器を使いこなせるかどうかが、デジタル信号処理アプリケーション構築に際してとても重要な要素となります。

FPGA に乗算器が搭載されていることを知りながら、きちんと活用していないケースもあるようです。乗算器はとても簡単に利用できるので、積極的に使用してみてください。